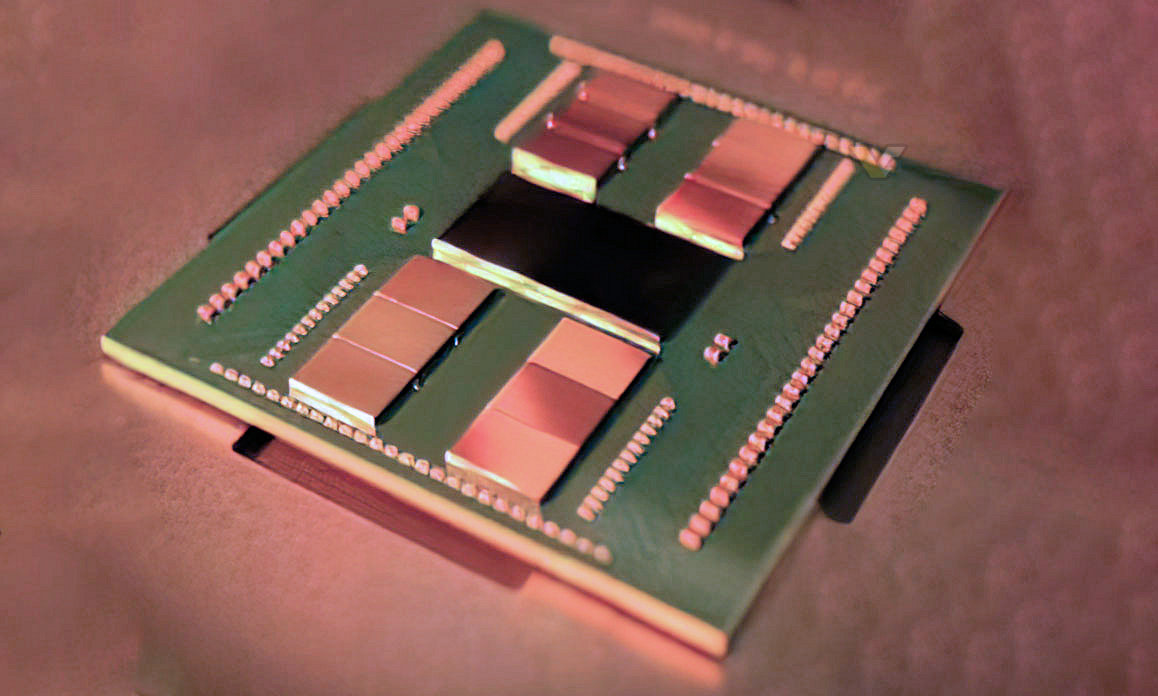

AMD Epyc Genoa con 12 chiplets en la foto

Solo ayer Ha aparecido la primera foto del nuevo zócalo SP5 (LGA6096), y ahora finalmente podemos ver el procesador EPYC de próxima generación sin el disipador térmico integrado.

Una foto de un supuesto procesador EPYC Génova fue compartido en TF AMD (Top Talent) en Malasia. Es la primera fotografía que muestra los 12 chiplets instalados en el paquete SP5. Lo que es importante tener en cuenta aquí es que lo más probable es que se trate de una maqueta y que la fotografía tenga al menos 10 meses de antigüedad (a juzgar por cuándo se publicó).

CPU AMD EPYC “Genoa”, Fuente: AMD TF Malaysia/@Phatal187

EPYC Génova tiene hasta 96 núcleos y 192 subprocesos en su configuración completa. AMD lanzará muchos SKU con núcleos parcialmente deshabilitados, por lo que el hecho de que este procesador tenga 12 chipsets no significa que tendrá los 96 núcleos activos.

Cada matriz Zen4 CCD tiene un área de 72 mm², que es 8 mm² más pequeña que la Zen3 (como en la serie EPYC “Milan”). La matriz de E/S también es más pequeña, alrededor de 397 mm² en comparación con los 416 mm² de las CPU Zen3 EPYC. Dicho esto, AMD no tuvo problemas para instalar 6 chipsets en cada lado de la matriz de E/S, teniendo en cuenta que el paquete SP5 (LGA 6096) también es un 37 % más grande que el SP3.

CPU AMD EPYC “Genoa”, Fuente: AMD TF Malaysia/@Phatal187

La nueva plataforma SP5 de AMD admitirá memoria DDR5 de hasta 12 canales, así como una interfaz PCIe Gen5. AMD Genoa ya está enviando a los primeros clientes, según AMD. La nueva serie EPYC 7004 está ahora en camino de ser lanzada a finales de este año.

| Especificaciones de la serie de procesadores RUMORED AMD EPYC | ||||||

|---|---|---|---|---|---|---|

| VideoCardz | 7001 “Nápoles” | 7002 “Roma” | 7003 “Milán” 7003 “Milán-X” |

7004 “Génova” | 7004 “Bérgamo” | |

| 7005 “Turín” | Tirar | 2017 | 2019 | 2021 | 2022 | 2022 |

| 2023/2024 | Arquitectura | Zen de 14nm | 7nmZen2 | 7nmZen3 | 5nmZen4 | 5nmZen4c |

| Zen5 | Enchufe | SP3 (LGA4094) | SP3 (LGA4094) | SP3 (LGA4094) | SP5 (LGA-6096) | SP5 (LGA-6096) |

| SP5 (LGA-6096) | Módulos / Chiplets | 4xCCD | 8xCCD + 1xIOD | 8xCCD + 1xIOD | 12xCCD + 1xIOD | 12xCCD + 1xIOD |

| Para confirmar | ||||||

| Núcleos máximos | reloj máximo | Para confirmar | Para confirmar | |||

| Para confirmar | Caché L2 por núcleo | 0,5 MB | 0,5 MB | 0,5 MB | 1 MB | Para confirmar |

| Para confirmar | Caché L3 por CCX | 8 MB | 8 MB | 32 MB/96 MB | 32 MB | |

| Para confirmar | ||||||

| Para confirmar | ||||||

| canales de memoria | soporte de memoria | carriles PCIe | ||||

| Para confirmar | Para confirmar | |||||

cTDP máxima Para confirmar Fuente: TF AMD Microelectrónica

vía @Phatal187

“Introvertido. Solucionador de problemas. Aficionado total a la cultura pop. Estudiante independiente. Creador”.