Por qué eso importa: La Ley de Moore ha estado en soporte vital durante algún tiempo, pero aún no está muerta. Los fabricantes de chips están quemando aceite de medianoche para miniaturizar los diseños de transistores, y un equipo de investigadores en China ha creado lo que se cree que es el más pequeño hasta el momento.

Durante varias décadas, los científicos e ingenieros han reducido los transistores hasta el punto en que sus características más pequeñas son solo docenas de átomos. Desde los primeros circuitos integrados en la década de 1950, la tasa de progreso en la miniaturización de transistores ha seguido la Ley de Moore, que predijo que la densidad de los componentes activos en los chips integrados se duplicaría cada dos años.

Como muchos de nuestros lectores saben, el progreso en esta dirección ha ralentizado significativamente en los últimos años. La razón principal es que nos estamos acercando rápidamente a los límites físicos de lo que es posible con los materiales existentes y los procesos de fabricación más avanzados que tenemos.

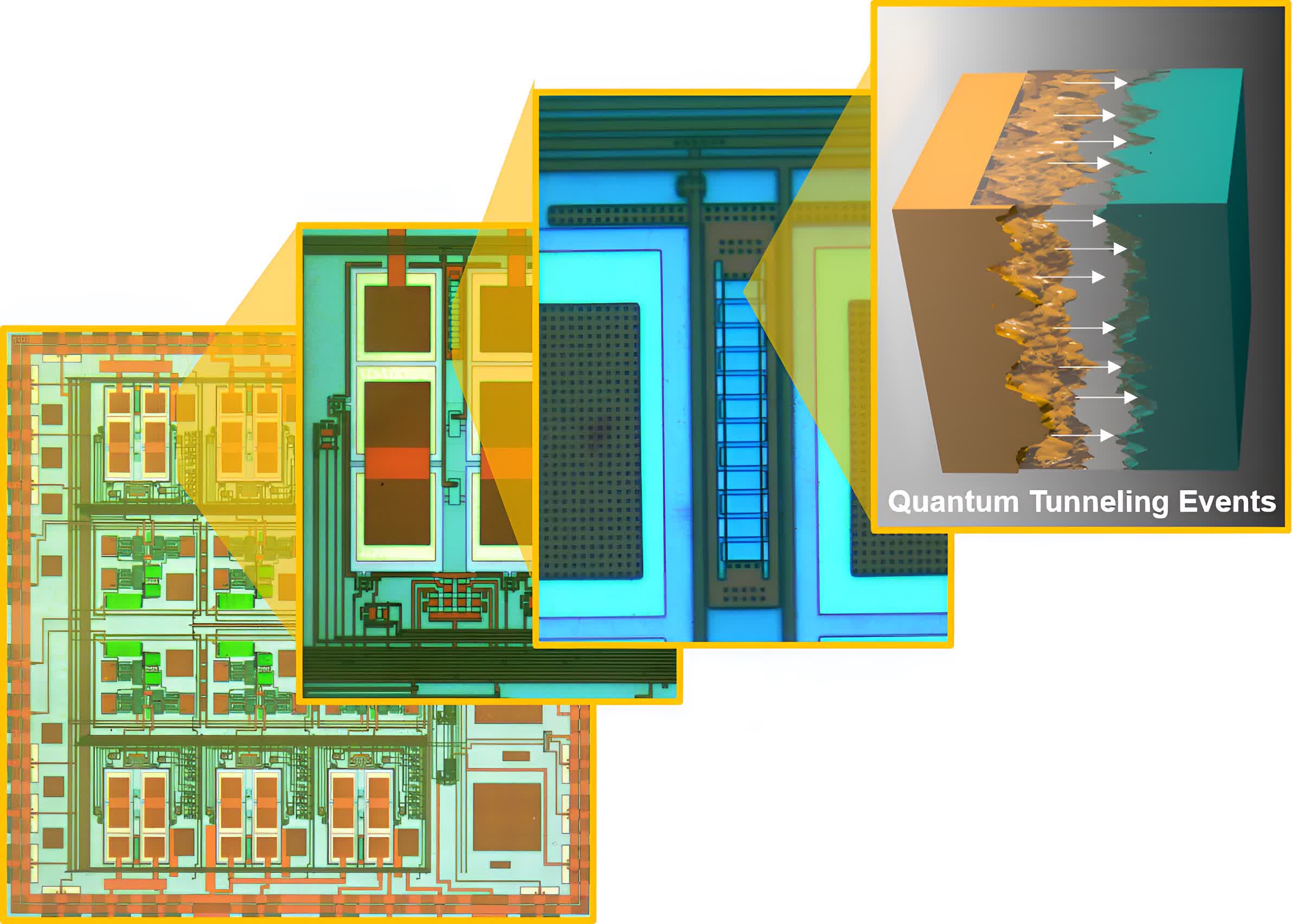

Más específicamente, no podemos hacer puertas de transistores, que controlan el flujo de corriente desde la fuente hasta el drenaje, mucho más pequeñas que 5 nm debido a algo llamado tunelización cuántica que les impide trabajar según lo previsto. Los materiales como el grafeno y los nanotubos de carbono pueden ser vitales para hacer transistores aún más pequeños gracias a sus propiedades físicas, pero se necesita tiempo para construir dispositivos funcionales.

en un papel publicado esta semana, investigadores chinos explican que han creado un transistor con la longitud de compuerta más corta jamás reportada. Este hito fue posible gracias a la utilización creativa de grafeno y disulfuro de molibdeno y apilándolos en una estructura de escalera de dos escalones.

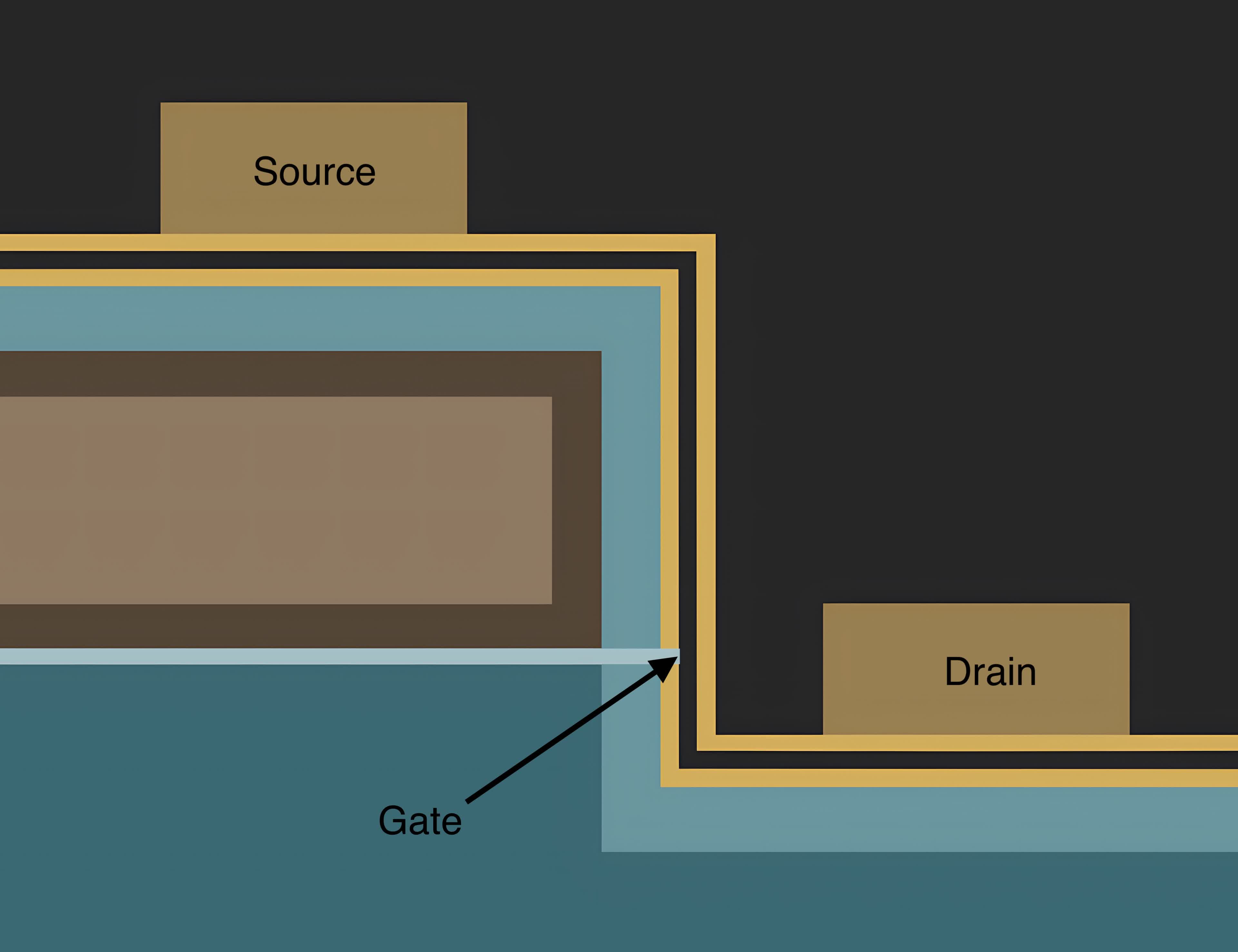

En el peldaño superior está la fuente y en el peldaño más bajo está el drenaje. Ambos están hechos de una aleación de titanio y paladio separados por la superficie de la escalera, que está hecha de una sola hoja de un material semiconductor llamado disulfuro de molibdeno, que descansa sobre una capa de dióxido de hafnio que actúa como aislante eléctrico.

El interior del escalón superior es literalmente un sándwich de aluminio cubierto de óxido de aluminio, que descansa sobre una lámina de grafeno, una sola capa de átomos de carbono. El óxido de aluminio actúa como aislante eléctrico, excepto por una pequeña abertura en la pared vertical del escalón superior, donde la lámina de grafeno puede entrar en contacto con el disulfuro de molibdeno. Toda la estructura de la escalera descansa sobre una gruesa capa de dióxido de silicio.

El truco de este proyecto es que se usa el borde de la hoja de grafeno, lo que significa que cuando la puerta se establece en el estado “encendido”, tiene solo 0,34 nm de ancho, esencialmente el ancho de la capa de grafeno. . Otra característica notable de este “transistor de pared lateral” es su fuga de corriente insignificante debido a la mayor resistencia fuera de estado. Los fabricantes pueden aprovechar esta cualidad para aplicaciones de bajo consumo. Lo mejor de todo es que sería relativamente fácil de hacer, aunque muchos de los prototipos requerían un poco de tensión para activarse.

Lea también: La máquina EUV de próxima generación de ASML le dará una nueva vida a la ley de Moore

La investigadora de la Universidad de Tsinghua, Tian-Ling Ren, fue coautora del estudio y dijo que este podría ser “el último nudo en la ley de Moore”. También cree que ir por debajo de 0,34 nm para el tamaño de puerta es casi imposible.

Por supuesto, los investigadores detrás del nuevo transistor acaban de demostrar que se puede fabricar un transistor que funcione utilizando materiales delgados de un átomo sin inventar un nuevo proceso para colocar con precisión las capas necesarias. Construir de forma fiable miles de millones de estos transistores de pared lateral sigue siendo un sueño lejano, pero es un paso fundamental en esa dirección, que alimenta la esperanza de dispositivos más rápidos y con mayor eficiencia energética en el futuro.

Mientras tanto, Samsung, Intel y TSMC están trabajando duro para hacer puerta general (GAA-FET) transistores una realidad y Estandarización interconexiones para diseños de chiplet.

“Introvertido. Solucionador de problemas. Aficionado total a la cultura pop. Estudiante independiente. Creador”.